УДК 681.518.5:004.052.32 DOI: 10.17586/0021-3454-2016-59-7-524-533

# МЕТОД ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ КОМБИНАЦИОННЫХ ЛОГИЧЕСКИХ УСТРОЙСТВ НА ОСНОВЕ КОДА "2 ИЗ 4"

В. В. Сапожников, Вл. В. Сапожников, Д. В. Ефанов

Петербургский государственный университет путей сообщения Императора Александра I, 190031, Санкт-Петербург, Россия

E-mail: TrES-4b@yandex.ru

Предложен метод построения систем функционального контроля, позволяющий уменьшать показатели их структурной избыточности по сравнению с известными способами. Решение найдено за счет использования при организации системы функционального контроля равновесных кодов. Предложена структурная схема системы функционального контроля комбинационных устройств, реализующая принцип логического дополнения булевых функций, на основе применения равновесного кода "2 из 4". Указаны особенности, которые необходимо учитывать при организации структур систем функционального контроля как на основе кода "1 из 4", так и на основе кода "2 из 4" с обеспечением свойства их полной самопроверяемости. Показаны преимущества использования кода "2 из 4" по сравнению кодом "1 из 4" при организации систем функционального контроля комбинационных устройств. В частности, отмечено, что для обеспечения свойства полной самопроверяемости системы функционального контроля на основе кода "2 из 4" требуются менее жесткие ограничения, чем при использовании для этих целей кода "1 из 4".

**Ключевые слова:** система функционального контроля, логическое дополнение, код "1 из 4", код "2 из 4", полностью самопроверяемая структура, тестирование

Введение. При построении дискретных систем, обеспечивающих обнаружение отказов, часто используются методы функционального (рабочего, on-line) контроля, позволяющие определять техническое состояние объекта диагностирования без отключения его от объектов управления [1]. При организации систем функционального контроля используются идеи помехоустойчивого кодирования — выходы контролируемой логической схемы отождествляются с информационным вектором заранее выбранного систематического кода или с кодовым словом неразделимого кода. От выбранного на этапе проектирования системы функционального контроля кода, в конечном итоге, зависят такие важные характеристики самой системы, как структурная избыточность, особенности обнаружения ошибок в контролируемом объекте, контролепригодность, быстродействие, энергопотребление и пр. В задачах организации систем функционального контроля логических схем автоматики и вычислительной техники

эффективно применение равновесных кодов с малой длиной кодовых слов (например, кодов "1 из 3", "1 из 4" и "2 из 4"). Тестеры таких кодов имеют максимально простую структуру и для обеспечения их полной самопроверяемости требуется минимальное число тестовых комбинаций [2].

В настоящей работе исследована возможность использования кодов "2 из 4" (2/4-кодов) при организации систем функционального контроля. Получаемые таким образом структуры систем функционального контроля имеют уменьшенную, по сравнению с применением кодов "1 из 4" (1/4-кодов), структурную избыточность.

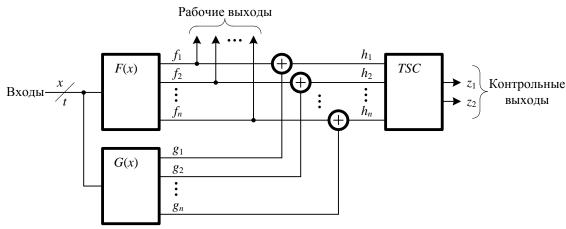

Система функционального контроля на основе равновесного кода "1 из 4". На рис. 1 приведена структурная схема системы функционального контроля комбинационных логиче-

ских устройств, которая исследовалась в работах [3—7]. Исходное комбинационное логическое устройство F(x) реализует систему булевых функций  $f_1, f_2, ..., f_n$  от t переменных  $x_1, x_2, ..., x_t$ . Для организации контроля устанавливается блок дополнения G(x), на выходах которого формируются функции дополнения  $g_1, g_2, ..., g_n$ . Каждая выходная функция основного блока  $f_i$  ( $i \in \{1; 2; ...; n\}$ ) преобразуется (дополняется) при помощи элемента XOR (сложение по модулю 2) и соответствующей функции  $g_i$  в специальную контрольную функцию  $h_i$  ( $h_i = f_i \oplus g_i$ ). В результате каждый выходной вектор  $\langle f_1 f_2 ... f_n \rangle$  блока F(x) преобразуется в вектор  $\langle h_1 h_2 ... h_n \rangle$ , который подается на вход тестера TSC. Функции  $g_1, g_2, ..., g_n$  выбираются таким образом, чтобы для каждого входного набора  $\langle x_1 x_2 ... x_t \rangle$  формировался вектор  $\langle h_1 h_2 ... h_n \rangle$ , принадлежащий некоторому выбранному коду. Тестер фиксирует факт принадлежности векторов этому коду. В работе [3] показано, что структура логического дополнения имеет ряд преимуществ по сравнению с традиционной структурой контроля комбинационных устройств, которая предусматривает формирование на выходах основного и дополнительного блоков кодовых векторов  $\langle f_1 f_2 ... f_n g_1, g_2, ..., g_n \rangle$ , принадлежащих некоторому систематическому

В этом случае блок G(x) вычисляет функции, соответствующие контрольным разрядам кодовых слов [8—12].

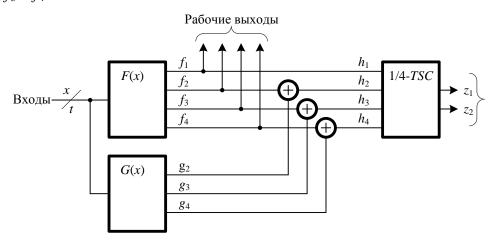

Puc. 1

В работах [3, 4, 6, 13—18] исследовано построение системы функционального контроля на основе применения 1/4-кода. Тестер 1/4-TSC имеет простую структуру [2] и требует для своей проверки всего четыре кодовых слова: {0001, 0010, 0100, 1000}. Для комбинационного устройства с четырьмя выходами система контроля приведена на рис. 2. Для преобразования векторов  $< f_1 f_2 f_3 f_4 >$  в векторы  $< h_1 h_2 h_3 h_4 > 1/4$ -кода достаточно дополнить только три функции  $f_2, f_3$  и  $f_4$ .

### Puc. 2

Для того чтобы схема рис. 2 была полностью самопроверяемой (ПСП-схемой) [1, 2], необходимо решить следующие три задачи:

- 1) определить такие функции дополнения  $g_2$ ,  $g_3$  и  $g_4$ , которые формируют на входе 1/4-TSC кодовые векторы, принадлежащие только 1/4-коду;

- 2) выбрать такие функции дополнения, при которых на вход 1/4-TSC поступают все четыре вектора проверяющего теста:  $\{0001, 0010, 0100, 1000\}$ ;

- 3) обеспечить поступление на входы каждого элемента XOR всех четырех возможных входных наборов  $\{00, 01, 10, 11\}$ , так как только в этом случае осуществляется полная проверка внутренней структуры элемента [19].

Покажем, что указанные задачи эффективно решаются при построении схемы логического дополнения на основе 2/4-кода.

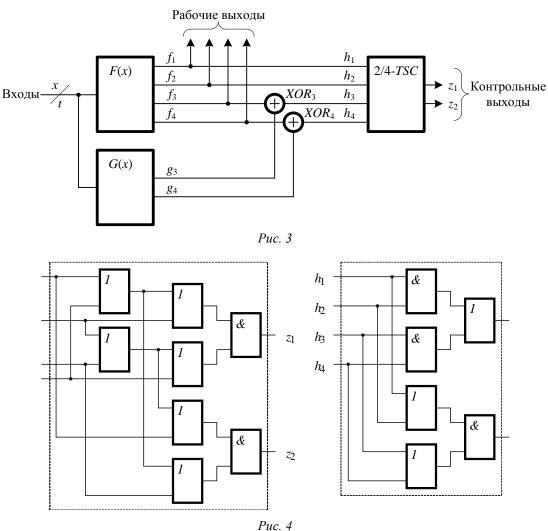

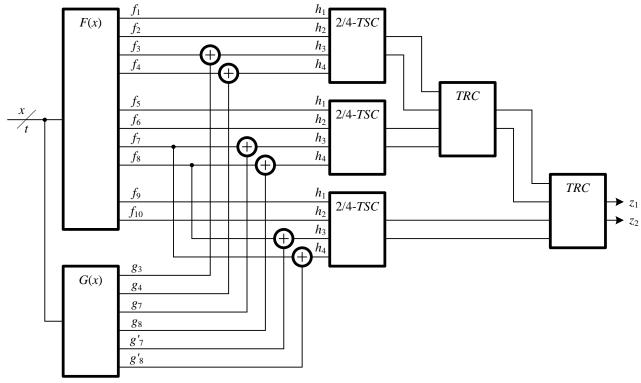

**Базовая структура логического дополнения для кода "2 из 4".** На рис. 3 приведена базовая структура, основанная на применении известной схемы 2/4-TSC с минимальной сложностью (схемы тестеров: рис. 4, a — 1/4-кода;  $\delta$  — 2/4-кода). Данная структура имеет следующие существенные преимущества по сравнению со структурой, основанной на применении 1/4-TSC. Сложность 2/4-TSC (6 двухвходовых элементов) меньше сложности 1/4-TSC (8 элементов) [2], а необходимое число проверяющих наборов у 2/4-TSC, которые представлены в табл. 1, такое же, как и у 1/4-TSC. Кроме того, в структуре рис. 3 дополняются только две функции ( $f_2$  и  $f_4$ ), поэтому она содержит меньшее число элементов XOR и в общем случае более простой блок G(x).

Таблица I

| проверяющие наобры для тестера 2/4-кода |       |       |       |       |       |  |  |

|-----------------------------------------|-------|-------|-------|-------|-------|--|--|

| $h_1$                                   | $h_2$ | $h_3$ | $h_4$ | $z_1$ | $z_2$ |  |  |

| 0                                       | 0     | 1     | 1     | 1     | 0     |  |  |

| 0                                       | 1     | 1     | 0     | 0     | 1     |  |  |

| 1                                       | 0     | 0     | 1     | 0     | 1     |  |  |

| 1                                       | 1     | 0     | 0     | 1     | 0     |  |  |

Из табл. 1 следует, что представленная на рис. 3 структура может быть построена в двух случаях:

1) система  $f_1$ — $f_4$  должна содержать две функции  $f_{i_1}$  и  $f_{i_2}$  (  $i_1,i_2\in\{1;2;3;4\}$  ) такие, что

$$\frac{f_{i_{1}}f_{i_{2}} \neq 0,}{f_{i_{1}}f_{i_{2}} \neq 0,}$$

$$\frac{f_{i_{1}}f_{i_{2}} \neq 0,}{f_{i_{1}}f_{i_{2}} \neq 0,}$$

$$\frac{f_{i_{1}}f_{i_{2}} \neq 0,}{f_{i_{1}}f_{i_{2}} \neq 0;}$$

(1)

2) система  $f_1$ — $f_4$  должна содержать две функции  $f_{i_1}$  и  $f_{i_2}$  (  $i_1,i_2\in \left\{1;2;3;4\right\}$  ) такие, что

$$\begin{cases}

f_{i_1} \overline{f_{i_2}} \neq 0, \\

f_{i_1} \overline{f_{i_2}} \neq \tilde{x}_1 \tilde{x}_2 \cdot \dots \cdot \tilde{x}_t, \\

\overline{f_{i_1}} f_{i_2} \neq 0, \\

\overline{f_{i_1}} f_{i_2} \neq \tilde{x}_1 \tilde{x}_2 \cdot \dots \cdot \tilde{x}_t.

\end{cases} \tag{2}$$

В табл. 2 приведены примеры систем функций  $f_1$ — $f_4$ . Условия (1) и (2) определяют возможность формирования на входах 2/4-TSC всех четырех проверяющих наборов (см. табл. 1) при условии дополнения только двух функций из четырех. В столбце 2 таблицы представлена система функций, отвечающая условиям (1). Эти условия означают, что имеются две функции (например,  $f_1$  и  $f_2$ ), которые хотя бы на одном входном наборе принимают одинаковые значения 00 и 11 и хотя бы на одном входном наборе принимают противоположные значения 01 и 10. Поэтому данные функции можно не дополнять, а выходы  $f_1$  и  $f_2$  блока F(x) можно соединить непосредственно с входами, например,  $h_1$  и  $h_2$  тестера. При этом можно обеспечить поступление на входы тестера всех четырех проверяющих векторов 0011, 1100, 1001 и 0110.

В столбце 3 таблицы представлена система функций, отвечающая условиям (2). Эти условия означают, что имеются две функции (например,  $f_1$  и  $f_2$ ), которые хотя бы на двух входных наборах принимают противоположные значения 01 и хотя бы на двух входных наборах принимают противоположные значения 10. Поэтому эти функции можно не дополнять,

а входы  $f_1$  и  $f_2$  блока F(x) можно соединить непосредственно с входами, например  $h_1$  и  $h_3$ .

В столбце 4 представлена система функций, которая не отвечает условиям (1) и (2), с целью организации контроля такая система может быть преобразована путем инвертирования одной или нескольких функций  $f_i$ . При этом инверторы устанавливаются на входах 2/4-TSC. Так система, расположенная в столбце 4, преобразуется в систему, расположенную в столбце 5, путем инвертирования функции  $f_1$ . При этом выполняются условия (2).

Таблица 2 Іримеры систем функций, реализуемых блоком F(x)

| примеры систем функции, реализуемых олоком $F(x)$ |                |                |                |                |  |  |  |  |

|---------------------------------------------------|----------------|----------------|----------------|----------------|--|--|--|--|

| $x_1 x_2 x_3$                                     | $f_1f_2f_3f_4$ | $f_1f_2f_3f_4$ | $f_1f_2f_3f_4$ | $f_1f_2f_3f_4$ |  |  |  |  |

| 1                                                 | 2              | 3              | 4              | 5              |  |  |  |  |

| 000                                               | 1110           | 0101           | 1111           | 0111           |  |  |  |  |

| 001                                               | 1110           | 0010           | 1111           | 0111           |  |  |  |  |

| 010                                               | 0001           | 0000           | 0100           | 1100           |  |  |  |  |

| 011                                               | 1000           | 0010           | 0111           | 1111           |  |  |  |  |

| 100                                               | 1000           | 1000           | 0010           | 1010           |  |  |  |  |

| 101                                               | 0010           | 1000           | 0010           | 1010           |  |  |  |  |

| 110                                               | 0111           | 0000           | 0011           | 1011           |  |  |  |  |

| 111                                               | 0111           | 0100           | 0011           | 1011           |  |  |  |  |

Если не найдена система функций, отвечающая указанным условиям, задача контроля устройства методом логического дополнения на основе 2/4-кода всегда может быть решена в рамках структуры с дополнением трех или всех четырех функций.

Рассмотрим алгоритм вычисления функций дополнения на примере системы функций (табл. 3), которая удовлетворяет условиям (1). В таблице функции  $f_1$ — $f_4$  представлены в столбце 2. В столбце 3 показан первый этап вычисления функций  $h_1$ — $h_4$ . На этом этапе устанавливается равенство  $h_1$ = $f_1$ ,  $h_2$ = $f_2$ . Далее в строках 1 и 2, в которых  $f_1$ = $f_2$ =1, устанавливаются значения  $h_3$ = $h_4$ =00, а в строках 3 и 6, в которых  $f_1$ = $f_2$ =0, устанавливаются  $h_3$ = $h_4$ =1. Затем вычисляются значения функций  $g_3 = f_3 \oplus h_3$  и  $g_4 = f_4 \oplus h_4$ , которые показаны в столбце 4. Далее вычисляются входные наборы, поступление которых на элементы  $XOR_3$  и  $XOR_4$  обеспечивается на данном этапе алгоритма (столбец 5). На входы  $XOR_3$  обеспечена подача трех из четырех наборов: 11, 01, 10, а на входы  $XOR_4$ : 00, 11, 01.

Таблица 3 Результат анализа системы функций для построения контролепригодной системы ее функционального контроля

| No x₁3 |               |                | $h_1h_2h_3h_4$ | 8384 | $XOR_3$  | $XOR_4$  | $h_1h_2h_3h_4$ | 8384 | $XOR_3$  | $XOR_4$  | $h_1h_2h_3h_4$ | 8384 |

|--------|---------------|----------------|----------------|------|----------|----------|----------------|------|----------|----------|----------------|------|

|        | $x_1 x_2 x_3$ | $f_1f_2f_3f_4$ |                |      | $f_3g_3$ | $f_4g_4$ |                |      | $f_3g_3$ | $f_4g_4$ |                |      |

|        | 1             | 2              | 3              | 4    | 4        | 5        | 6              | 7    | 8        | 3        | 9              | 10   |

| 1      | 000           | 1110           | 1100           | 10   | 11       | 00       |                |      |          |          |                |      |

| 2      | 001           | 1110           | 1100           | 10   | 11       | 00       |                |      |          |          |                |      |

| 3      | 010           | 0001           | 0011           | 10   | 01       | 10       |                |      |          |          |                |      |

| 4      | 011           | 1000           | 10             |      |          |          |                |      |          |          | 1010           | 10   |

| 5      | 100           | 1000           | 10             |      |          |          | 1001           | 01   | 00       | 01       |                |      |

| 6      | 101           | 0010           | 0011           | 01   | 10       | 01       |                |      |          |          |                |      |

| 7      | 110           | 0111           | 01             |      |          |          | 0110           | 01   | 10       | 11       |                |      |

| 8      | 111           | 0111           | 01             |      |          |          |                |      |          |          | 0110           | 01   |

На следующем этапе рассматриваются строки 4 и 5, в которых  $f_1f_2$ =10. На одной из этих строк необходимо сформировать вектор  $h_1h_2h_3h_4$ =1001, который входит в проверяющий тест. Выбирается тот вариант, который обеспечивает поступение на входы элементов XOR новых проверяющих наборов. В данном случае выбирается строка 5 (см. столбец 6), при этом  $g_3$ =0 и  $g_4$ =1 (см. столбец 7), а на входе элемента  $XOR_3$  обеспечивается набор 00 (см. столбец 8). В результате на входах  $XOR_3$  обеспечен проверяющий тест.

Далее рассматриваются строки 7 и 8, в которых  $f_1f_2$ =01. На одной из этих строк необходимо сформировать вектор  $h_1h_2h_3h_4$ =0110, который входит в проверяющий тест. В данном случае выбирается строка 7 (см. столбец 6), при этом  $g_3$ =0 и  $g_4$ =1 (см. столбец 7).

На входах элемента  $XOR_4$  обеспечивается набор 11 (см. столбец 8). В результате на входах  $XOR_4$  также обеспечивается проверяющий тест.

Таким образом, обеспечено поступление всех четырех проверяющих наборов на вход 2/4-TSC и на оба элемента XOR.

В итоге оказались незаполненными две строки — 4 и 8. В них вносятся любые векторы  $h_1h_2h_3h_4$ , принадлежащие 2/4-коду. При этом заполнять строки целесообразно таким образом, чтобы получаемые функции логического дополнения имели максимально простую техническую реализацию (см. столбцы 9 и 10).

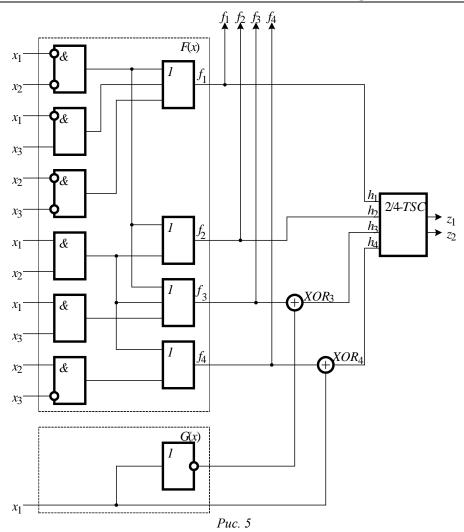

В результате получаем, что  $g_3 = \overline{x_1}$  и  $g_4 = x_1$ . В табл. 4 сведены результаты анализа системы функций, реализуемой блоком F(x):

$$\begin{cases} f_1 = \overline{x_1 x_2} \vee \overline{x_1 x_3} \vee \overline{x_2 x_3}; \\ f_2 = \overline{x_1 x_2} \vee x_1 x_2; \\ f_3 = \overline{x_1 x_2} \vee x_1 x_2 \vee x_1 x_3; \\ f_4 = x_1 x_2 \vee x_2 \overline{x_3}. \end{cases}$$

Для примера в табл. 4 также приводятся произвольные функции для организации контроля по 1/4-коду. Нетрудно заметить, что функции дополнения вектора функций  $f_1f_2f_3f_4$  до вектора 2/4-кода проще функций дополнения этого вектора до вектора 1/4-кода. Для тестеров обоих кодов в рассматриваемом примере удается получить полное множество проверяющих наборов.

На рис. 5 приведена система функционального контроля рассматриваемого комбинационного логического устройства.

Таблица 4

| Функции логического дополнения |                |                               |                |         |                |  |  |

|--------------------------------|----------------|-------------------------------|----------------|---------|----------------|--|--|

| $x_1x_2x_3$                    | $f_1f_2f_3f_4$ | ,                             | 2/4-код        | 1/4-код |                |  |  |

|                                |                | g <sub>3</sub> g <sub>4</sub> | $h_1h_2h_3h_4$ | 828384  | $h_1h_2h_3h_4$ |  |  |

| 000                            | 1110           | 10                            | 1100           | 110     | 1000           |  |  |

| 001                            | 1110           | 10                            | 1100           | 110     | 1000           |  |  |

| 010                            | 0001           | 10                            | 0011           | 000     | 0001           |  |  |

| 011                            | 1000           | 10                            | 1010           | 000     | 1000           |  |  |

| 100                            | 1000           | 01                            | 1001           | 000     | 1000           |  |  |

| 101                            | 0010           | 01                            | 0011           | 000     | 0010           |  |  |

| 110                            | 0111           | 01                            | 0110           | 011     | 0100           |  |  |

| 111                            | 0111           | 01                            | 0110           | 110     | 0001           |  |  |

Назовем функции  $f_i, f_j \in \{f_1; f_2; f_3; f_4\}$ , для которых выполняются условия (1) или (2), основными в базовой структуре логического дополнения на основе 2/4-кода. Для заданной системы функций таких пар основных функций может быть несколько. Например, для функции в табл. 3 кроме  $(f_1, f_2)$  парами основных функций являются  $(f_1, f_3), (f_1, f_4), (f_2, f_4), (f_3, f_4)$ . Для каждой пары могут быть рассчитаны свои функции дополнения.

Для каждой пары  $(f_i, f_j)$  всегда решается задача формирования всех четырех проверяющих наборов на входе 2/4-TSC, поэтому основная проблема состоит в формировании таких наборов на входах XOR. Но так как в структуре имеется только два таких элемента, эта задача

решается путем простого перебора вариантов. Если для рассматриваемой пары основных функций решения нет, то рассматривается другая пара основных функций.

Если комбинационное устройство имеет более четырех выходов, целесообразно отдельно контролировать четверки выходов, как это предложено в работе [14]. Можно также предложить использовать одни и те же выходы в разных четверках (рис. 6).

Puc. 6

Заключение. В статье отмечены неоспоримые преимущества структуры системы функционального контроля методом логического дополнения на основе 2/4-кода по сравнению со структурой на основе 1/4-кода. Основным преимуществом является то, что к системе функций  $f_1$ — $f_4$  предъявляются менее жесткие требования по обеспечению полной проверки элементов XOR. Для 1/n-кода эти требования сформулированы в п. 3 теоремы о необходимых и достаточных условиях построения ПСП-схемы контроля на основе логического дополнения [14]. В частности, необходимо, чтобы число рабочих входных наборов, на которых заданы функции, было как минимум в два раза больше числа выходов схемы. Для 2/4-кода это требование не является необходимым. Например, если в системе, рассмотренной в табл. 3, исключить входные наборы 011 и 111 (при этом число рабочих входных наборов становится равным 6, что меньше удвоенного числа выходов логического устройства), полученные в таблице функции дополнения обеспечивают построение ПСП-схемы контроля.

## СПИСОК ЛИТЕРАТУРЫ

- 1. Пархоменко П. П., Согомонян Е. С. Основы технической диагностики (оптимизация алгоритмов диагностирования, аппаратурные средства). М.: Энергоатомиздат, 1981. 320 с.

- 2. Сапожников В. В., Сапожников Вл. В. Самопроверяемые дискретные устройства. СПб: Энергоатомиздат, 1992. 224 с.

- 3. *Goessel M., Saposhnikov VI., Saposhnikov V., Dmitriev A.* A new method for concurrent checking by use of a 1-out-of-4 code // Proc. of the 6<sup>th</sup> IEEE Intern. On-line Testing Workshop. Palma de Mallorca, Spain, July 3—5, 2000. P. 147—152.

- 4. *Сапожников В. В., Сапожников Вл. В., Дмитриев А. В., Морозов А. В., Гессель М.* Организация функционального контроля комбинационных схем методом логического дополнения // Электронное моделирование. 2002. Т. 24, № 6. С. 51—66.

- 5. *Гессель М., Морозов А. В., Сапожников В. В., Сапожников Вл. В.* Логическое дополнение новый метод контроля комбинационных схем // Автоматика и телемеханика. 2003. № 1. С. 167—176.

- 6. Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D. New Methods of Concurrent Checking. Dordrecht: Springer Science+Business Media B.V., 2008. 184 p.

- 7. Das D. K., Roy S. S., Dmitiriev A., Morozov A., Gössel M. constraint don't cares for optimizing designs for concurrent checking by 1-out-of-3 codes // Proc. of the 10th Intern. Workshops on Boolean Problems. Freiberg, Germany, September, 2012. P. 33—40.

- 8. *Nicolaidis M.*, *Zorian Y.* On-line testing for VLSI a compendium of approaches // J. of Electronic Testing: Theory and Applications. 1998. N 12. P. 7—20.

- 9. *Mitra S.*, *McClaskey E. J.* Which concurrent error detection scheme to choose? // Proc. of Intern. Test Conf. Atlantic City, NJ, USA, 3—5 October 2000. P. 985—994.

- 10. *Matrosova A. Yu.*, *Levin I.*, *Ostanin S. A.* Self-checking synchronous FSM network design with low overhead // VLSI Design. 2000. Vol. 11, Is. 1. P. 47—58.

- 11. *Ефанов Д. В., Сапожников В. В., Сапожников Вл. В.* О свойствах кода с суммированием в схемах функционального контроля // Автоматика и телемеханика. 2010. № 6. С. 155—162.

- 12. *Сапожников В. В., Сапожников Вл. В., Ефанов Д. В.* Применение кодов с суммированием при синтезе систем железнодорожной автоматики и телемеханики на программируемых логических интегральных схемах // Автоматика на транспорте. 2015. Т. 1, № 1. С. 84—107.

- 13. Saposhnikov V. V., Saposhnikov Vl. V., Morozov A., Osadtchi G., Gossel M. Design of totally self-checking combinational circuits by use of complementary circuits // Proc. of East-West Design & Test Workshop. Yalta, Ukraine, 2004. P. 83—87.

- 14. *Гессель М., Морозов А. В., Сапожников В. В., Сапожников Вл. В.* Контроль комбинационных схем методом логического дополнения // Автоматика и телемеханика. 2005. № 8. С. 161—172.

- 15. Sen S. K., Roy S. S. An optimized concurrent self-checker using constraint-don't cares and 1-out-of-4 code // National Conf. (AECDISC-2008). As ansol Engineering College, 1—2 August 2008.

- 16. Sen S. K., Roy S. S. A self-checking circuit for concurrent checking by 1-out-of-4 code with design optimization using constraint don't cares // National Conf. on Emerging trends and advances in Electrical Engineering and Renewable Energy (NCEEERE 2008). Sikkim Manipal Institute of Technology, Sikkim, 22—24 December 2008.

- 17. *Halder S., Roy S. S., Sen S. K.* An optimized concurrent self-checker using constraint-don't cares and 1-out-of-4 code // National Conf. (AECDISC-2010). As ansol Engineering College, 1—2 August 2010.

- 18. Sen S. K. A self-checking circuit for concurrent checking by 1-out-of-4 code with design optimization using constraint don't cares // National Conf. on Emerging trends and advances in Electrical Engineering and Renewable Energy (NCEEERE 2010). Sikkim Manipal Institute of Technology, Sikkim, 22—24 December 2010.

- 19. *Аксёнова Г. П.* Необходимые и достаточные условия построения полностью проверяемых схем свертки по модулю 2 // Автоматика и телемеханика. 1979. № 9. С. 126—135.

#### Сведения об авторах

## Валерий Владимирович Сапожников

д-р техн. наук, профессор; Петербургский государственный университет путей сообщения Императора Александра I, кафедра автоматики и телемеханики на железных дорогах;

E-mail: port.at.pgups@gmail.com

Владимир Владимирович Сапожников

д-р техн. наук, профессор; Петербургский государственный университет путей сообщения Императора Александра I, кафедра автоматики и телемеханики на железных дорогах;

E-mail: at.pgups@gmail.com

Дмитрий Викторович Ефанов

канд. техн. наук; Петербургский государственный университет путей сообщения Императора Александра I, кафедра автоматики и телемеханики на железных дорогах;

E-mail: TrES-4b@yandex.ru

Рекомендована кафедрой автоматики и телемеханики на железных дорогах

Поступила в редакцию 21.03.16 г.

Ссылка для цитирования: Сапожников В. В., Сапожников Вл. В., Ефанов Д. В. Метод функционального контроля комбинационных логических устройств на основе кода "2 из 4" // Изв. вузов. Приборостроение. 2016. T. 59, № 7. C. 524—533.

### METHOD OF OPERATION CONTROL OVER COMBINATORY LOGIC DEVICE BASED ON 2-OUT-OF-4 CODE

V. V. Sapozhnikov, VI. V. Sapozhnikov, D. V. Efanov

Emperor Alexander I St. Petersburg State Transport University, 190031, St. Petersburg, Russia E-mail: TrES-4b @yandex.ru

A new method of operational control system design is developed. The method allows diminishing the system redundancy index as compared with the known approaches. The solution is obtained due to application of balanced codes in creation of operation control system. The proposed structural diagram of the control system realizes the principle of logical complement of Boolean functions based on the use of 2-out-of-4 code. Special features to be taken into account in design of the structure of an operation control system on the base of 1-out-of-4 or 2-out-of-4 codes providing the total self-checking are considered. Advantages of the use of 2-out-of-4 code over 1-out-of-4 code for combinatory logic device control system are demonstrated. In particular, provision of total self-checking of the operation control system on the base of 2-out-of-4 code requires less stringent restrictions than in the case when 1-out-of-4 code is applied.

Keywords: concurrent error detection, logical complement, 1-out-of-4 code, 2-out-of-4 code, totally self-checking structure, testing

#### Data on authors

Valery V. Sapozhnikov - Dr. Sci., Professor; Emperor Alexander I St. Petersburg State Transport University, Department of Automation and Remote Con-

trol on Railways; E-mail: port.at.pgups@gmail.com

Dr. Sci., Professor; Emperor Alexander I St. Petersburg State Vladimir V. Sapozhnikov Transport University, Department of Automation and Remote Con-

trol on Railways; E-mail: at.pgups@gmail.com

Dmitry V. Efanov PhD; Emperor Alexander I St. Petersburg State Transport University, Department of Automation and Remote Control on Railways; E-

mail: TrES-4b@yandex.ru

For citation: Sapozhnikov V. V., Sapozhnikov VI. V., Efanov D. V. Method of operation control over combinatory logic device based on 2-out-of-4 code // Izv. vuzov. Priborostroenie. 2016. Vol. 59, N 7. P. 524-533 (in Russian).

DOI: 10.17586/0021-3454-2016-59-7-524-533