УДК 004.272

DOI: 10.17586/0021-3454-2019-62-6-524-533

# МЕТОД ПАРАЛЛЕЛЬНО-КОНВЕЙЕРНО-ПАРАЛЛЕЛЬНОЙ КОММУТАЦИИ ПАКЕТОВ В МУЛЬТИПРОЦЕССОРАХ

МОХАММЕД ДЖАМИЛЬ АБДО АЖМАЛЬ, И. В. ЗОТОВ, Г. И. ПЕРЕДЕЛЬСКИЙ

Юго-Западный государственный университет, 305040, Курск, Россия E-mail: zotovigor@yandex.ru

Рассмотрена задача повышения скорости работы и пропускной способности коммуникационной среды мультипроцессора при использовании коммутационных устройств с входными FIFO-буферами и выходной матрицей регистров. Предложен метод коммутации пакетов в мультипроцессорах, новизна которого заключается в параллельно-конвейерной загрузке пакетов в матрицу регистров из входных буферов без ожидания выдачи всех ранее загруженных пакетов. Рассмотрена структурная модель коммутационного устройства, реализующего разработанный метод. Сформулирован алгоритм обработки пакетов коммутационным устройством, основанный на представлении множества пакетов, находящихся в матрице регистров в каждом такте работы устройства, графом совместности, отражающим возможность одновременной выдачи пакетов на выходы. Представлено правило взвешивания вершин графа совместности, учитывающее время нахождения пакетов в матрице регистров. Показано, что выбор множества пакетов, подлежащих выдаче, можно свести к выделению клики графа совместности, обладающей наибольшим весом, что позволяет минимизировать время обработки пакетов. Выведена формула для оценки среднего времени прохождения пакета через матрицу регистров коммутационного устройства при использовании разработанного метода. Исследованы зависимости указанного времени от числа входов/выходов устройства, выполнен их сравнительный анализ для предлагаемого метода и метода параллельнопоследовательной коммутации пакетов. Показано, что разработанный метод позволяет снизить среднее время прохождения пакета через матрицу регистров более чем на 41 % во всех практически значимых случаях.

**Ключевые слова:** мультипроцессор, коммуникационная среда, коммутация пакетов, аппаратные средства, конвейерный режим

Введение. Скорость работы и пропускная способность коммутационных устройств (КУ) существенно влияют на время передачи данных в мультипроцессорах (МП) [1] и время обращения процессоров к удаленной памяти, а следовательно, на производительность мультипроцессора в целом. Применяемые в МП коммутационные устройства используют режим коммутации пакетов и во многом подобны АТМ-коммутаторам вычислительных сетей, абонентских систем и мультикомпьютеров [2]. Их основным отличием является то, что пакеты разбиваются на фрагменты одинаковой разрядности (flit), которые передаются по шинам в параллельном коде за один-два такта. Указанные фрагменты могут группироваться [3] либо передаваться независимо друг от друга [4—6].

Применяемые в мультипроцессорах КУ различаются, прежде всего, расположением внутренних буферов, необходимых для временного хранения передаваемых пакетов. КУ с входными буферами [7, 8] не предъявляют требований к скорости работы коммутирующей части и, как правило, обладают квадратичной аппаратной сложностью, что позволяет использовать их при большом числе входов/выходов. Однако доказано [9], что подобные КУ (без модификации дисциплин обслуживания буферов и/или применения особых способов организации коммутирующей части) не могут обеспечить пропускную способность выше

$2-\sqrt{2}\approx0,586$  из-за возникновения блокировок пакетов в головных регистрах буферов (HOL blocking). Наибольшая пропускная способность (до 100~%) теоретически достигается в КУ с выходными буферами [10, 11]. В подобных КУ пакеты сразу перераспределяются между выходами и затем сохраняются в буферах, что исключает блокировку пакетов. Однако такие КУ характеризуются кубической аппаратной сложностью и предъявляют серьезные требования к скорости работы коммутирующей части, которая должна в n раз превышать интенсивность потока пакетов на входе устройства (где n — число входов/выходов КУ). Поэтому их применение возможно при небольшом числе входов/выходов n и/или при условии снижения интенсивности трафика.

На практике часто используются комбинированные (с входным и выходным расположением внутренних буферов) варианты построения КУ. К ним, в частности, относятся коммутаторы с комбинированными очередями [12], с виртуальными выходными очередями [13—15], параллельно-конвейерные [16]. Перспективным представляется также параллельно-последовательный способ организации КУ с входными буферами и выходной матрицей регистров [17]. Он характеризуется квадратичной аппаратной сложностью и имеет простую коммутирующую часть, включающую несколько мультиплексоров и демультиплексоров. Однако известная реализация этого способа [18] не позволяет достичь требуемых значений пропускной способности КУ и характеризуется невысокой скоростью работы коммутирующей части, поскольку не допускает загрузку в матрицу регистров новых пакетов до завершения выдачи ранее загруженных.

В настоящей статье предлагается метод параллельно-конвейерно-параллельной коммутации пакетов в мультипроцессорах (ПКП-метод), являющийся развитием метода параллельно-последовательной коммутации (ПП-метода) [17], обеспечивающий повышение скорости работы и пропускной способности КУ при сохранении его квадратичной аппаратной сложности. Приводится аппаратно-ориентированный алгоритм параллельно-конвейерно-параллельной коммутации пакетов, реализующий предлагаемый метод; выполняется сравнительная оценка времени прохождения пакета через матрицу регистров при использовании параллельно-последовательной и параллельно-конвейерно-параллельной коммутации пакетов.

**Ключевые особенности предлагаемого метода.** Разработанный метод предполагает разделение буферизующей части КУ на входную часть (входные FIFO-буферы) и матрицу регистров (МР). FIFO-буферы подключены к соответствующим столбцам МР, что позволяет копировать пакеты из различных буферов в матрицу регистров параллельно. Пакеты распределяются между строками МР согласно алгоритму маршрутизации. Выдача пакетов из матрицы регистров на соответствующие выходы КУ осуществляется в параллельно-последовательном режиме: пакеты, находящиеся в разных строках МР, выдаются параллельно; пакеты, размещенные в одной и той же строке, передаются на выход последовательно.

Разработанный метод включает следующие этапы: 1) определение направлений выдачи пакетов, находящихся в головных ячейках входных буферов, в соответствии с реализуемым алгоритмом маршрутизации; 2) загрузка в МР всех пакетов, которым соответствуют свободные регистры матрицы, сдвиг очередей пакетов в буферах, откуда были считаны эти пакеты; 3) анализ способа размещения множества пакетов в МР и определение оптимального порядка выдачи пакетов из строк матрицы; 4) выдача выбранного множества пакетов из матрицы регистров на выходы КУ и освобождение соответствующих регистров.

Важной особенностью предлагаемого метода является то, что очередное множество пакетов загружается в MP сразу после перезаписи предыдущего (в следующем такте) без ожидания полного освобождения матрицы (этап 2). При этом если в некоторой строке MP более одного пакета, то первым выдается тот, который дольше всех пакетов этой же строки находился в матрице (этап 3). Если таких пакетов несколько, выбор осуществляется случайным образом согласно равномерному закону распределения.

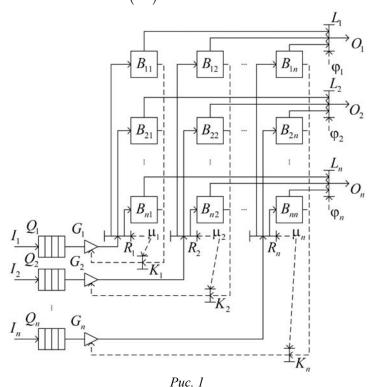

Структурная модель коммутационного устройства. Структурная модель КУ, реализующего разработанный метод, приведена на рис. 1. Устройство содержит входы  $I_1, I_2, \dots, I_n$ , выходы  $O_1, O_2, ..., O_n$ , входные буферы  $Q_1, Q_2, ..., Q_n$ , матрицу регистров  $B = \|B_{ij}\|$ ,  $i, j = \overline{1, n}$ , а также коммутирующие элементы  $R_1, R_2, \dots, R_n$ ,  $K_1, K_2, \dots, K_n$ ,  $L_1, L_2, \dots, L_n$  и клапаны  $G_1, G_2, ..., G_n$  . Буферы  $Q_1, Q_2, ..., Q_n$  обеспечивают прием и временное хранение пакетов с входов  $I_1,I_2,\ldots,I_n$  соответственно. Матрица регистров B служит для перераспределения пакетов согласно реализуемому алгоритму маршрутизации и перед их выдачей на выходы  $O_1, O_2, \dots, O_n$ . Выбор строки матрицы для записи пакета, считанного из буфера  $Q_i$ , определяется правилом  $\mu_i$ , которое реализуется коммутирующим элементом  $R_i$ . Пакеты выдаются на  $O_i$  последовательно в течение нескольких тактов ретрансляции, причем порядок выдачи определяется правилом  $\phi_i$ , которое реализуется коммутирующим элементом  $L_i$ . Клапаны  $G_1, G_2, ..., G_n$  служат для временной блокировки передачи пакетов из соответствующих буферов при занятости требуемых регистров матрицы В. Такая организация КУ позволяет загружать пакеты из FIFO-буферов в матрицу регистров по мере возможности, без ожидания завершения выдачи ранее загруженных пакетов. При этом из рис. 1 видно, что структурная (аппаратная) сложность КУ составляет  $O(n^2)$ .

**Алгоритм коммутации пакетов.** Определим индикаторную функцию s такую, что  $s(Q_l)=1$ , если в буфере  $Q_l$  в данный момент времени имеется хотя бы один пакет, и  $s(Q_l)=0$ , если  $Q_l$  пуст. Пусть  $F_k$  — множество пакетов, находящихся в матрице B на k-м такте работы КУ,  $k=0,1,2,\ldots$ . На множестве  $\left\{B_{ij}\right\}$  определим индикаторную функцию  $S_k$ , такую, что  $S_k\left(B_{ij}\right)=c_q$ , если регистр  $B_{ij}$  содержит некоторый пакет  $c_q$  в k-м такте,  $S_k\left(B_{ij}\right)=\varnothing$ , если  $B_{ij}$  свободен.

Puc. 2

На множестве пакетов  $F_k$  определим отношение совместности  $\alpha_k \subseteq F_k \times F_k$  , такое, что

$$\left(c_{q},c_{r}\right)\in\alpha_{k}\Leftrightarrow c_{q}\in\bigcup_{j=1}^{n}S_{k}\left(B_{i'j}\right),c_{r}\in\bigcup_{j=1}^{n}S_{k}\left(B_{i''j}\right)\colon i'\neq i''.$$

Введем в рассмотрение граф  $\Gamma_k = \langle F_k, \alpha_k \rangle$ , вершины которого соответствуют пакетам множества  $F_k$ , а ребра отображают их совместность. Взвесим вершины графа  $\Gamma_k$  неотрицательными целыми числами  $\{\tau_q\}$ . Вес  $\tau_q$  вершины  $c_q$  будем определять временем, которое пакет  $c_q$  провел в MP с момента загрузки, выраженным в числе тактов работы КУ. Сразу после записи пакета  $c_q$  в матрицу полагаем  $\tau_q = 0$ . Выделим в графе  $\Gamma_k$  подмножество  $\Gamma_k' = \langle F_k', \alpha_k' \rangle$ ,  $F_k' \subseteq F_k$ ,  $\alpha_k' \subseteq \alpha_k$  такое, что  $\sum_{c_q \in F_k'} \tau_q = \max$ . Если таких подмножеств в графе

$\Gamma_k$  несколько, то выберем любое случайным образом. По определению, носитель  $F_k'$  подмножества  $\Gamma_k'$  будет включать только совместные вершины и будет максимальным по включению.

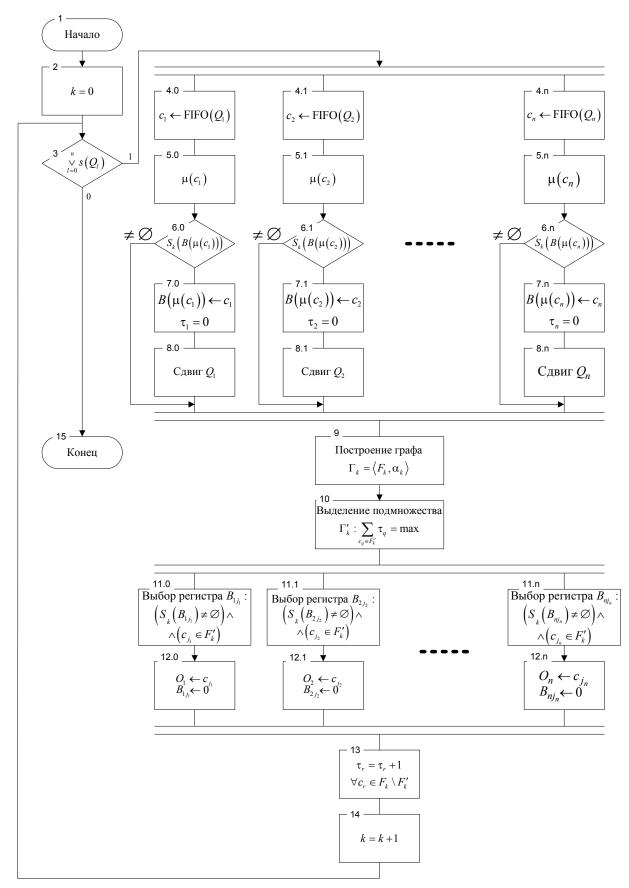

Представленные выше построения позволяют сформулировать алгоритм параллельноконвейерно-параллельной коммутации пакетов. Граф-схема алгоритма изображена на рис. 2 (через ← на рис. 2 обозначена операция чтения содержимого регистра и записи значения в регистр).

**Оценка времени прохождения пакета через матрицу регистров.** Время прохождения пакета через MP напрямую влияет на скоростные характеристики и пропускную способность КУ. Его можно оценить, рассматривая всевозможные варианты распределения пакетов в матрице.

Обозначим через t минимально возможное время прохождения пакета через MP (время последовательного прохождения одного пакета через пустую MP). Тогда среднее время прохождения пакета через MP в параллельно-конвейерно-параллельном KУ составит:

$$t_{\Pi K\Pi} = \frac{t}{n} \sum_{l=1}^{n} l P_{\overline{n}}^{l}, \tag{1}$$

где  $\overline{n}$  — среднее число пакетов, находящихся в MP в данном такте работы КУ:  $\overline{n} = \overline{n}' + \overline{n}''$ ,  $\overline{n} \ge n$ ;  $\overline{n}'$  — среднее число пакетов, которые в данном такте удается переписать из буферов в матрицу с учетом занятости некоторых ее регистров ( $\overline{n}' \le n$ );  $\overline{n}''$  — среднее число пакетов, не выданных в предыдущих тактах и все еще находящихся в MP ( $\overline{n}'' \le \frac{n(n-1)}{2}$ );

$P_{\overline{n}}^{l}$  — вероятность того, что  $\overline{n}$  пакетов располагаются в матрице регистров так, что хотя бы в одной из ее строк находится l пакетов, а в остальных — не более l пакетов (в предположении о равновероятном распределении пакетов любого столбца между строками MP):

$$P_{\overline{n}}^{l} = \frac{Q_{\overline{n}}^{l}}{Q_{\overline{n}}},\tag{2}$$

где  $Q_{\overline{n}}$  — число всевозможных способов размещения  $\overline{n}$  пакетов в MP;  $Q_{\overline{n}}^l$  — число способов размещения  $\overline{n}$  пакетов в матрице таким образом, что хотя бы в одной из ее строк l пакетов, а в остальных — не более l:

$$Q_{\overline{n}} = \sum_{i=1}^{n} Q_{\overline{n}}^{i} . \tag{3}$$

Значения  $Q_{\overline{n}}^l$  могут быть получены по следующей рекуррентной формуле:

Значения

$$Q_{\overline{n}}^l$$

могут быть получены по следующей рекуррентной формуле:

$$Q_{\overline{n}}^l \equiv Q_{\overline{n}}^l \left( p, n \right) = \begin{cases} 0 & \text{при } \left( p + l - 1 > \overline{n} \right) \lor \left( pl < \overline{n} \right); \\ n^p & \text{при } l = 1; \\ \left\lfloor \frac{\overline{n}}{l} \right\rfloor \\ \sum_{i = \max\{1, \, \overline{n} \bmod p\}} \xi \left[ \left( C_n^l \right)^i C_p^i \sum_{r=1}^{\min\{l-1, \, \overline{n} - il\}} Q_{\overline{n} - il}^r \left( p - i, n \right) \right] \text{при } l = \overline{2, n-1}, \end{cases}$$

(4)

где  $\lfloor a \rfloor$  — целая часть числа a;  $C_x^y = \frac{x!}{y!(x-y)!}$  — число бесповторных сочетаний из x эле-

ментов по у; р — число строк текущей подматрицы МР, оно уменьшается по мере вычисления (изначально считается  $p \equiv n$ ); дополнительная функция  $\xi$  определяется следующим обра-30M:

$$\xi(x) = \begin{cases} x, & \text{если } \overline{n} - il \ge p - i; \\ 0, & \text{если } \overline{n} - il (5)$$

Использование функции  $\xi$  позволяет заранее исключить ветви дерева рекуррентных вычислений, в которых будут нарушены условия размещения пакетов в МР. Например, при  $p \equiv n = 4$ ,  $\bar{n} = 5$  и l = 2 пакеты невозможно разместить в MP так, чтобы не осталось пустых строк.

Среднее время прохождения пакета через МР при параллельно-последовательной коммутации, согласно [18]:

$$t_{\Pi\Pi} = \frac{t}{n} \sum_{l=1}^{n} l P_n^l, \tag{6}$$

где  $P_n^l$  — вероятность того, что n пакетов разместятся в MP так, что хотя бы в одной из строк окажется l пакетов, а в остальных строках будет не более l пакетов (в предположении о равновероятном распределении пакетов любого столбца между строками МР):

$$P_n^l = \frac{Q_n^l}{Q_n},\tag{7}$$

где  $Q_n$  — число всевозможных способов размещения n пакетов в MP;  $Q_n^l$  — число способов размещения n пакетов в матрице таким образом, что хотя бы в одной из строк окажется l пакетов, а в остальных строках будет не более l:

$$Q_n = n^n, (8)$$

$$Q_{n}^{l} \equiv Q_{n}^{l}(p) = \begin{cases} 1 & \text{при } l = 0; \\ A_{p}^{n} & \text{при } l = 1; \\ p & \text{при } l = n; \\ \left[ \sum_{i=1}^{n} \left[ \left( \prod_{j=0}^{i-1} C_{n-jl}^{l} \right) C_{p}^{i} \chi \left( \sum_{r=1}^{\min\{l-1, n-il\}} Q_{n-il}^{r}(p-i) \right) \right] & \text{при } l = \overline{2, n-1}, \end{cases}$$

$$(9)$$

где p — число строк в текущей подматрице регистров (первоначально  $p \equiv n$ );  $A_x^y = \frac{x!}{(x-y)!}$  — число бесповторных размещений из x элементов по y;  $\chi(a)$  — дополнительная функция:  $\chi(a) = a$ , если a > 0;  $\chi(a) = 1$  — иначе.

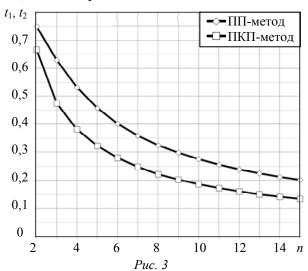

На рис. 3 приведены зависимости величин  $t_{\Pi K\Pi}$  и  $t_{\Pi \Pi}$  от n, полученные с использованием формул (1)—(5) и (6)—(9) соответственно. Результаты расчетов по формулам (1)—(5) показали, что величина  $t_{\Pi K\Pi}$  весьма слабо зависит от  $\overline{n}-n$ , поэтому в качестве  $t_{\Pi K\Pi}$  для каждого n бралось усредненное значение по всем допустимым  $\overline{n}>n$ . Единицей измерения величин  $t_{\Pi K\Pi}$  и  $t_{\Pi \Pi}$  является такт длительности t (т.е. минимально возможное время последовательного физического прохождения пакета через MP). Тот факт, что величины  $t_{\Pi K\Pi}$  и  $t_{\Pi \Pi}$  принимают значения, меньшие t, связан с эффектом ускорения вследствие параллельной обработки сразу нескольких пакетов. Так, например, для ретрансляции n=5 пакетов при использовании разработанного метода требуется примерно 1,61t временных единиц (что в  $5/1,61\approx3,1$  раза быстрее, чем при последовательной обработке). При этом на каждый пакет в среднем приходится лишь 0,32215t временных единиц.

Из рис. З видно, что предложенный метод имеет преимущества по времени прохождения пакета через MP перед параллельно-последовательным методом при любых значениях n. Минимальное преимущество составляет 12,5 % (при n=2). Отметим, однако, что случаи n<5 не типичны для мультипроцессоров рассматриваемого класса и поэтому практически не значимы. В практически значимых случаях ( $n \ge 5$ ) согласно рис. З предложенный метод ускоряет прохождение пакетов через MP более чем на 41 %, по сравнению с ПП-методом. Так, при n=5 (что соответствует системам с двумерной матричной топологией) ускорение составляет примерно 41,9 %, при n=7 (системы с организацией трехмерного тора) получаем преимущество примерно в 44,5 %, при n=9 (системы с топологией четырехмерного гиперкуба) имеется ускорение в 46,4 %.

Заключение. Ускорение прохождения пакетов через матрицу регистров ведет к повышению скорости работы и пропускной способности коммутационного устройства, однако теоретическая оценка общего эффекта затруднительна из-за необходимости учета случайного характера параметров входящих потоков пакетов. В связи с этим для оценки полного времени ретрансляции пакета, скорости работы и пропускной способности КУ при использовании ПП- и ПКП-методов целесообразно перейти к имитационному моделированию.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Jerraya A. A., Wolf W. et al. Multiprocessor systems-on-chips. Elsevier Inc., 2005.

- 2. Misra S., Goswami S. Network routing: fundamentals, applications, and emerging technologies. Wiley Telecom, 2014.

- 3. Tilera: Tile processor architecture overview for the TILE-GX series [Электронный ресурс]: <a href="http://www.mellanox.com/repository/solutions/tile-scm/docs/UG130-ArchOverview-TILE-Gx.pdf">http://www.mellanox.com/repository/solutions/tile-scm/docs/UG130-ArchOverview-TILE-Gx.pdf</a>.

- 4. *Olofsson* A. Epiphany-V: A 1024 processor 64-bit RISC System-On-Chip [Электронный ресурс]: <a href="https://www.parallella.org/docs/e5\_1024core\_soc.pdf">https://www.parallella.org/docs/e5\_1024core\_soc.pdf</a>>.

- 5. Pat. 8531943 B2 USA. Mesh network / A. Olofsson. Sep. 10, 2013.

- 6. *Chen Y.* Cell switched network-on-chip candidate for billion-transistor system-on-chips // 2006 IEEE Intern. SOC Conf. 2006. P. 57—60.

- 7. Karol M., Hluchyj M. Queueing in high-performance packet switching // IEEE J. on Selected Areas in Communications. 1988. Vol. 6. Dec. P. 1587—1597. DOI: 10.1109/49.12886.

- 8. *Ganjali Y., Keshavarzian A., Shah D.* Cell switching versus packet switching in input-queued switches // IEEE/ACM Transactions on Networking. 2005. Vol. 13, N 4. Aug. P. 782—789. DOI: 10.1109/TNET.2005.852884.

- 9. *Karol M., Hluchyj M., Morgan S.* Input versus output queueing on a space-division packet switch // IEEE Transactions on Communications. 1987. Vol. 35, N 12. P. 1347—1356. DOI: 10.1109/TCOM.1987.1096719.

- 10. Chen D. X., Mark J. W. SCOQ: a fast packet switch with shared concentration and output queueing // IEEE/ACM Transactions on Networking. 1993. Vol. 1, N 1. P. 142—151. DOI: 10.1109/90.222914.

- 11. *Dong Z., Rojas-Cessa R., Oki E.* Buffered Clos-network packet switch with per-output flow queues // Electronics Letters. 2011. Vol. 47, N 1. P. 32—34. DOI: 10.1049/el.2010.2677.

- 12. Chuang S.-T., Goel A., McKeown N., Prabhakar B. Matching output queueing with a combined input/output-queued switch // IEEE J. on Selected Areas in Communications. 1999. Vol. 17, N 6. P. 1030—1039. DOI: 10.1109/49.772430.

- 13. Kang K., Park K.-J., Sha L., Wang Q. Design of a crossbar VOQ real-time switch with clock-driven scheduling for a guaranteed delay bound // Real-Time Systems. 2013. Vol. 49, N 1. P. 117—135. DOI: 10.1007/s11241-012-9169-6.

- 14. *Neely M. J., Modiano E., Cheng Y.-S.* Logarithmic delay for NxN packet switches under the crossbar constraint // IEEE/ACM Transactions on Networking. 2007. Vol. 15, N 3. P. 657—668. DOI: 10.1109/TNET.2007.893876.

- 15. Chang C.-S., Lee D.-S., Yue C.-Y. Providing guaranteed rate services in the load balanced Birkhoff-von Neumann switches // IEEE/ACM Transactions on Networking. 2006. Vol. 14, N 3. P. 644—656. DOI: 10.1109/TNET.2006.876202.

- 16. *Крикунов О. В.* и др. Коммутационный процессор с параллельно-конвейерной обработкой сообщений // Телекоммуникации. 2006. № 10. С. 11—16.

- 17. *Емельянов С. Г., Зотов И. В., Титов В. С.* Архитектура параллельных логических мультиконтроллеров. М.: Высш. школа, 2009. 233 с.

- 18. Беляев Ю. В. Параллельно-последовательный коммутатор для систем параллельной и распределенной обработки данных: Автореф. дис. ... канд. техн. наук. Курск, 2003. 17 с.

## Сведения об авторах

Мохаммед Джамиль Абдо Ажмаль

аспирант; Юго-Западный государственный университет, кафедра информационных систем и технологий; E-mail: gamal12345@mail.ru

Игорь Валерьевич Зотов

д-р техн. наук, профессор; Юго-Западный государственный университет, кафедра информационных систем и технологий;

E-mail: zotovigor@yandex.ru

Геннадий Иванович Передельский

д-р техн. наук, профессор; Юго-Западный государственный университет, кафедра электроснабжения;

E-mail: kafedra@yandex.ru

Поступила в редакцию 24.12.18 г.

**Ссылка** для **цитирования:** *Ажмаль Мохаммед Джамиль Абдо, Зотов И. В., Передельский Г. И.* Метод параллельно-конвейерно-параллельной коммутации пакетов в мультипроцессорах // Изв. вузов. Приборостроение. 2019. Т. 62, № 6. С. 524—533.

#### METHOD OF PARALLEL-PIPELINE-PARALLEL PACKET COMMUTATION IN MULTIPROCESSOR

## Mohammed Ajmal Jamil Abdo, I.V. Zotov, G. I. Peredelsky

Southwest State University, 305040, Kursk, Russia E-mail: zotovigor@yandex.ru

The problem of increasing the speed and throughput of multiprocessor communication networks using input FIFO-queued switches with an output register matrix is under consideration. A packet switching method is proposed featuring a parallel packet transfer pipeline which makes it possible to load packets from the input buffers to the register matrix with no delay needed to spin until the matrix is empty. The proposed method is shown to provide parallel and concurrent packet processing in the input and output circuits of the packet switch. A structural model of a packet switching unit based on the proposed approach is presented. A packet switching algorithm is formulated based on the representation of the set of packets loaded into the register matrix in the form of a packet consistency graph reflecting the packet set ability of being issued in parallel. A graph vertex weight assignment rule is stated taking into account the idle time packets spend in the register matrix. A maximum total weight clique of the consistency graph is shown to be searched for to pick up a proper subset of packets that can be issued currently which makes it possible to reduce the idle time. A formula is deduced to calculate the average time needed for a packet to be transferred through the register matrix of a switch based on the proposed method. The average packet transfer time versus the number of input/output terminals graphs are investigated and the comparison is made for the parallel-sequential switching method and the proposed approach. The developed method is demonstrated to decrease the average packet transfer time by 41 % for all cases of practical significance.

Keywords: multiprocessor, communication network, packet switching, hardware, pipeline mode

#### **REFERENCES**

- 1. Jerraya A.A., Wolf W. et al. Multiprocessor systems-on-chips, Elsevier Inc., 2005.

- 2. Misra S., Goswami S. *Network routing: fundamentals, applications, and emerging technologies*, Wiley Telecom, 2014.

- 3. *Tilera: Tile processor architecture overview for the TILE-GX series*, http://www.mellanox.com/repository/solutions/tile-scm/docs/UG130-ArchOverview-TILE-Gx.pdf.

- 4. Olofsson A. *Epiphany-V: A 1024 processor 64-bit RISC System-On-C*hip, https://www.parallella.org/docs/e5\_1024core\_soc.pdf.

- 5. Patent 8531943 B2 USA, Mesh network, Olofsson A. Published Sep. 10, 2013.

- 6. Chen Y. 2006 IEEE International SOC Conference, 2006, pp. 57-60.

- Karol M., Hluchyj M. IEEE Journal on Selected Areas in Communications, 1988, vol. 6, Dec., pp. 1587–1597.

DOI: 10.1109/49.12886.

- 8. Ganjali Y., Keshavarzian A., Shah D. IEEE/ACM Transactions on Networking, 2005, no. 4(13), pp. 782–789. DOI: 10.1109/TNET.2005.852884.

- Karol M., Hluchyj M., Morgan S. IEEE Transactions on Communications, 1987, no. 12(35), pp. 1347–1356.

DOI: 10.1109/TCOM.1987.1096719.

- 10. Chen D.X., Mark J.W. *IEEE/ACM Transactions on Networking*, 1993, no. 1(1), pp. 142–151. DOI: 10.1109/90.222914.

- 11. Dong Z., Rojas-Cessa R., Oki E. *Electronics Letters*, 2011, no. 1(47), pp. 32–34. DOI: 10.1049/el.2010.2677.

- 12. Chuang S.-T., Goel A., McKeown N., Prabhakar B. *IEEE Journal on Selected Areas in Communications*, 1999, no. 6(17), pp. 1030–1039. DOI: 10.1109/49.772430.

- 13. Kang K., Park K.-J., Sha L., Wang Q. *Real-Time Systems*, 2013, no. 1(49), pp. 117–135. DOI: 10.1007/s11241-012-9169-6

- 14. Neely M.J., Modiano E., Cheng Y.-S. *IEEE/ACM Transactions on Networking*, 2007, no. 3(15), pp. 657–668. DOI: 10.1109/TNET.2007.893876.

- 15. Chang C.-S., Lee D.-S., Yue C.-Y. *IEEE/ACM Transactions on Networking*, 2006, no. 3(14), pp. 644–656. DOI: 10.1109/TNET.2006.876202.

- 16. Krikunov O.V. et al. Telekommunikatsii, 2006, no. 10, pp. 11-16. (in Russ.)

- 17. Emel'yanov S.G., Zotov I.V., Titov V.S. *Arkhitektura parallel'nykh logicheskikh mul'tikontrollerov* (Architecture of Parallel Logic Multicontrollers), Moscow, 2009, 233 p. (in Russ.)

- 18. Belyayev Yu.V. Parallel'no-posledovatel'nyy kommutator dlya sistem parallel'noy i raspredelennoy obrabotki dannykh (Parallel-Serial Switch for Parallel and Distributed Data Processing Systems), Extended abstract of candidate's thesis. Kursk, 2003, 17 p. (in Russ.)

### Data on authors

Post-Graduate Student; Southwest State University, Department Mohammed J. A. Ajmal of Information Systems and Technologies; E-mail: gamal12345@mail.ru

Dr. Sci., Professor; Southwest State University, Department of Igor V. Zotov

Information Systems and Technologies; E-mail: zotovigor@yandex.ru

Dr. Sci., Professor; Southwest State University, Department of Gennady I. Peredelsky

Power Supply; E-mail: kafedra@yandex.ru

For citation: Ajmal Mohammed Jamil Abdo, Zotov I. V., Peredelsky G. I. Method of parallel-pipeline-parallel packet commutation in multiprocessor. Journal of Instrument Engineering. 2019. Vol. 62, N 6. P. 524—533 (in Russian).

DOI: 10.17586/0021-3454-2019-62-6-524-533