## ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА

УДК 004.31

### Е. А. Титенко, Е. А. Семенихин

# БЫСТРОДЕЙСТВУЮЩИЙ АРБИТР ОБРАБОТКИ ЗАПРОСОВ БОЛЬШОЙ РАЗРЯДНОСТИ

Предложен способ параллельно-конвейерной обработки запросов большой разрядности, описана техническая реализация арбитра.

Ключевые слова: арбитр, конвейер, параллельные вычисления.

Введение. Производительность вычислительных систем с массовым параллелизмом (многомашинные комплексы и многопроцессорные системы) определяется, прежде всего, согласованной работой коллектива процессоров над решением задач, имеющих альтернативные или множественные варианты выполнения [1]. Общая производительность таких систем зависит от многих факторов: типа модели вычислений, количества процессоров и их наращиваемости, ресурсной поддержки распараллеливания, организации памяти, обработки конфликтов за общий ресурс, организации системы коммутации, синхронизации готовности процессов по данным и др. [2].

В настоящей работе рассматривается задача согласования работы множества процессоров, направленного на уменьшение времени разрешения конфликтов между процессорами, запрашивающими общий ресурс. Общим ресурсом можно считать, например, разделяемую оперативную память, общую кэш-память, единый коммутатор-распределитель, ассоциативную память и др. При ограниченном объеме общего ресурса возникает задача выделения приоритетного запроса и первоочередного предоставления ресурса процессору, выставляющему такой запрос. Для решения данной задачи проектируется аппаратный быстродействующий арбитр на основе таких принципов, как параллелизм и конвейеризация вычислений в пределах операционной части устройства-арбитра.

**Постановка задачи и цель работы.** Аппаратный быстродействующий арбитр рассматривается как единое устройство (черный ящик), получающее на вход запросы (вектор запросов) и выдающее после обработки двоичное слово подтверждений (вектор подтверждений), содержащее единственную логическую "1" для найденного приоритетного запроса. В работе принимается модель вычисления приоритетной логической "1" в соответствии со статическими весами запросов, которые выставляют процессоры на получение общего ресурса. Отличительная особенность проектируемого быстродействующего арбитра связана с ориентацией на большую разрядность двоичного слова запросов n (n > 64) и созданием технического решения, обеспечивающего эффективный поиск приоритетной логической "1" за счет обработки не весовых двоичных данных.

**Общий подход к решению.** Предлагаемый подход к проектированию быстродействующего арбитра заключается в разработке структуры устройства, в котором процесс выделения приоритетной (старшей) логической "1" из входного двоичного слова запросов разби-

вается на ряд пространственно распределенных процессов поиска приоритетной логической "1" в каждом из выделенных локальных слов. Данные локальные слова последовательно примыкают друг к другу, образуя двоичное слово запросов. Особенность подхода состоит в том, что разбиение происходит автоматически, вычисляется начальное значение (стартовая точка) для каждого отдельного процесса, что определяет их самостоятельность и позволяет параллельно обрабатывать локальные слова.

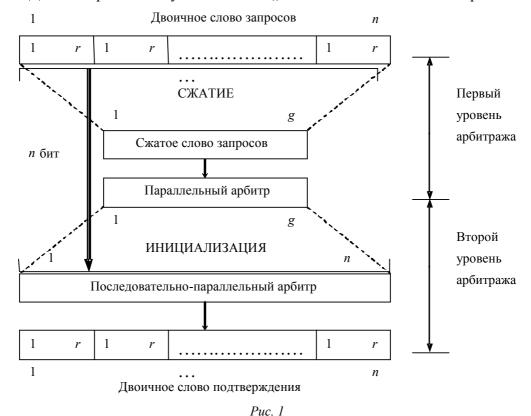

**Проектирование быстродействующего арбитра.** На рис. 1 приведена общая схема процесса арбитража при большой разрядности двоичного слова запросов n. В работе предлагается двухуровневая организация процесса арбитража: на первом уровне выполняется вычисление стартовых точек по входному двоичному слову запросов. Двоичное слово запросов разрядностью в n бит разбивается на g групп (локальных слов), каждая группа разрядностью r бит. Данный процесс получил название "сжатие двоичного слова запросов".

Сжатое слово запросов разрядностью g бит подлежит обработке параллельным арбитром, схема которого для малых значений разрядности известна [3, 4] и не является предметом рассмотрения настоящей статьи.

Работа параллельного арбитра заключается в выделении приоритетной логической "1" в сжатом g-разрядном слове запросов. Все биты полученного g-разрядного сжатого слова запросов являются стартовыми точками для параллельно выполняемых процессов арбитража второго уровня вычислений. На втором уровне осуществляется параллельная обработка локальных слов разрядностью r бит и формируется выходное двоичное слово подтверждений разрядностью n бит. Для параллельно-конвейерной обработки локальных слов разбитое по g группам значение входного двоичного слова запросов передается в параллельно-последовательный арбитр вместе с вычисленными стартовыми точками на первом уровне. В целом данная общая схема арбитража определяет конвейеризированную структуру вычислений, т.е. разбиение общего процесса вычислений на более мелкие уровни, совмещение во времени их

выполнения и выделение для каждого уровня структурно самостоятельного функционального узла [5].

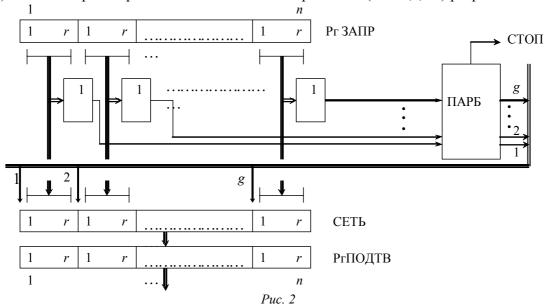

Структурная схема быстродействующего арбитра приведена на рис. 2 и содержит:

- 1) входной n -разрядный регистр запросов (РгЗАПР);

- 2) r-разрядные элементы ИЛИ для сжатия двоичного слова запросов по g группам и получения сжатого g-разрядного слова запросов;

- 3) параллельный арбитр (ПАРБ), обрабатывающий д-разрядное слово запросов;

- 4) параллельно-последовательный арбитр итеративную сеть арбитража (СЕТЬ) для выполнения параллельно-последовательного процесса арбитража по g группам, каждая группа разрядностью r бит;

- 5) выходной регистр двоичного слова подтверждений ( $Pr\PiOДTB$ ) разрядностью n бит.

При обнаружении нулевого значения сжатого слова запросов на ПАРБ быстродействующий арбитр выдает сигнал СТОП, прекращая обработку текущего двоичного слова запросов. При ненулевом значении сжатого g-разрядного слова запросов осуществляется его обработка в функциональном узле ПАРБ. Особенность ПАРБ в том, что за счет нерегулярности схемы время вычислений в данном функциональном узле не зависит от разрядности g, оно определяется временем обработки  $\tau$ =const одного разряда. На выходе ПАРБ формируется промежуточное g-разрядное слово стартовых точек, содержащее единственную логическую "1" в j-й позиции. Выделенная логическая "1" в j-й позиции инициирует обработку j-й группы разрядностью r бит из входного слова запросов на параллельно-последовательном арбитре. Таким образом, промежуточное g-разрядное слово стартовых точек является вторым операндом для параллельно-последовательного арбитра, принимающим на обработку как первый операнд r-разрядные группы из входного двоичного слова запросов (рис. 2).

Параллельно-последовательный арбитр организован как комбинационная схема — итеративная сеть арбитража (СЕТЬ), осуществляющая последовательное выделение приоритетной логической "1" в пределах группы начиная со значения стартовой точки. Если значение j-й стартовой точки нулевое (j=1-g), то СЕТЬ формирует нулевое значение j-й группы в составе выходного двоичного слова подтверждений. Среди стартовых точек существует такая k-я точка ( $k \in 1-g$ ), имеющая значение логической "1", которая задает в СЕТИ последовательный процесс арбитража в пределах k-й группы.

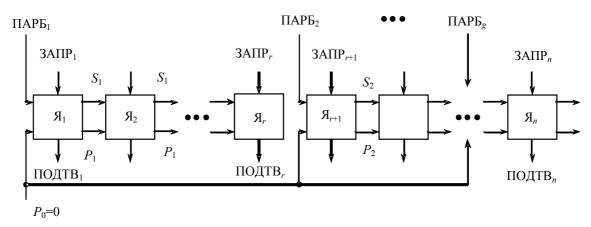

Итеративная сеть арбитража (рис. 3) представляет собой одномерный массив n ячеек, разбитых на g групп по r разрядов в каждой группе. С точки зрения нисходящего проекти-

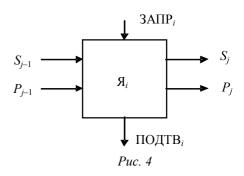

рования ячейка  $\mathfrak{A}_i$  (i=1-n) СЕТИ представляется черным ящиком, имеющим три входа и три выхода (рис. 4). Работа СЕТИ по выделению приоритетной логической "1" основана на параллельной работе g групп ячеек и последовательном поиске старшей логической "1" в пределах каждой группы.

Puc. 3

Функционирование отдельной ячейки обработки бита двоичного слова запросов  $3A\Pi P_i$  с учетом значения стартовой точки, вычисляемой ПАРБ для j-й группы ( j=1-g ), сводится к

вычислению бита выходного двоичного слова подтверждений  $\Pi O Д T B_i$  (i=1-n). Работа ячейки  $S_i$  описывается таблицей истинности ( $S_{j-1}$  — входной бит инициализации поиска приоритетной логической "1" в j-й группе, причем  $S_0 = \Pi A P B_j$  — стартовая точка поиска для j-й группы;  $S_j$  — выходной бит инициализации поиска приоритетной логической "1" в j-й группе,  $P_{j-1}$  — входной признак обнаружения приоритетной логической

"1" в j-й группе,  $P_0 = 0$  для всех g групп;  $P_j$  — выходной признак обнаружения приоритетной логической "1" в j-й группе).

Таблица истинности ячейки поиска приоритетной логической "1"

| No | $S_{j-1}$ | $P_{j-1}$ | $3A\Pi P_i$ | $S_i$ | $P_{i}$ | ПОДТВі |

|----|-----------|-----------|-------------|-------|---------|--------|

| 0  | 0         | 0         | 0           | 0     | 0       | 0      |

| 1  | 0         | 0         | 1           | 0     | 0       | 0      |

| 2  | 0         | 1         | 0           | 0     | 0       | 0      |

| 3  | 0         | 1         | 1           | 0     | 0       | 0      |

| 4  | 1         | 0         | 0           | 1     | 0       | 0      |

| 5  | 1         | 0         | 1           | 1     | 1       | 1      |

| 6  | 1         | 1         | 0           | 1     | 1       | 0      |

| 7  | 1         | 1         | 1           | 1     | 1       | 0      |

Данная таблица имеет следующую интерпретацию. При  $S_{j-1}=0$  (первые четыре строки таблицы) поиск приоритетной логической "1" не инициализируется, поэтому формируются нулевые значения  $P_j$  и  $\Pi O \not \Pi T B_i$ . При  $S_{j-1}=1$  поиск по j-й группе инициализируется, значение выходного бита  $\Pi O \not \Pi T B_i$  определяется значением признака обнаружения приоритетной логической "1" в данной группе, т.е. значением  $P_{j-1}$ . Если такой признак не был установлен в "1", то  $\Pi O \not \Pi T B_i=3A\Pi P_i$  (четвертая и пятая строки по номерам таблицы). Одновременно с

этим (при  $3A\Pi P_i = I$ ) выходной признак устанавливается как  $P_j = I$ , запрещая тем самым последующее выделение логических "1" в выходном слове подтверждений в пределах j-й группы (последние две строки таблицы).

**Заключение.** Таким образом, в результате проектирования разработан быстродействующий арбитр, ориентированный на обработку двоичных слов запросов большой разрядности (n > 64) и позволяющий совместить во времени процесс выделения приоритетной логической "1" за счет организации пространственно распределенных по длине двоичного слова запросов параллельно-конвейерных вычислений. Данное устройство может найти применение в потоковых вычислительных системах [6], в ассоциативных процессорах числовой и символьной обработки данных [1, 7], в информационно-поисковых системах и системах обработки знаний при разрешении конфликтов [8].

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Корнеев В. В. Следующее поколение суперкомпьютеров // Открытые системы. 2008. № 8. С. 14—19.

- 2. Хорошевский В. Г. Архитектура вычислительных систем. М.: Изд-во МГТУ им. Баумана, 2005. 512 с.

- 3. Потемкин И. С. Функциональные узлы цифровой автоматики. М.: Энергоатомиздат, 1988. 320 с.

- 4. Самофалов К. Г. и др. Цифровые ЭВМ. Теория и проектирование. Киев: Высш. школа, 1989. 423 с.

- 5. Кравец О. Я., Подвальный Е. С., Титов В. С., Ястребов А. С. Архитектура вычислительных систем с элементами конвейерной обработки: Учеб. пособие. СПб: Политехника, 2009. 152 с.

- 6. Стемпковский А. Л., Левченко Н. Н., Окунев А. С., Цветков В. В. Параллельная потоковая вычислительная система дальнейшее развитие архитектуры и структурной организации вычислительной системы с автоматическим распределением ресурсов // Информационные технологии. 2008. № 10. С. 2—7.

- 7. Воеводин В. В., Воеводин Вл. В. Параллельные вычисления. СПб: БХВ-Петербург, 2002. 599 с.

- 8. *Фельдман В. М.* Вычислительная система реального времени для реализации программ управления сложными объектами // Информационные технологии. 2009. № 2. С. 2—8.

### Сведения об авторах

**Евгений Анатольевич Титенко** — канд. техн. наук, доцент; Курский государственный технический университет, кафедра программного обеспечения вычислительной техни-

ки; E-mail: bossjohn@mail.ru

**Евгений Анатольевич Семенихин** — аспирант; Курский государственный технический университет, кафедра программного обеспечения вычислительной техники;

E-mail: bossjohn@mail.ru

Рекомендована кафедрой программного обеспечения вычислительной техники

Поступила в редакцию 04.06.10 г.